为了更好帮助学校科研团队开展优秀成果的宣传与推介,加速学校科技成果转化运用,中山大学科技园将持续征集并发布学校优秀科技成果。

成果一:一种基于异步单轨的流水线处理器

所属领域

微电子技术

成果简介

随着物联网和人工智能的快速发展,SOC技术不断成熟,现在的芯片大部分都集成了自己的处理器,可见处理器在电子技术中扮演着重要角色,因此处理器的设计受到广泛的关注。处理器结构大致为运算逻辑部件、寄存器部件和控制部件,这些部件都是由大量的寄存器构成,数据处理指令只对寄存器进行操作。由于全局时钟的存在,虽然运算速度和执行效率很高,但是寄存器始终随时钟不停的翻转,消耗了更多能量,增加了额外的功耗。此外,由于处理器大多是同步电路设计,全局时钟偏移问题严重,存在复杂的时钟树网络,设计比较困难,而且时钟树将会严重占用芯片设计面积和功耗。同时,在同步电路中,所有路径都在同一时钟下工作,为了保证一个时钟周期能够完成所有逻辑运算,时钟频率会被电路中的关键路径延时限制,同时影响到其它路径,而且关键路径的优化很困难,因此时钟频率难以提高,限制了整个处理器的性能。因此,现有的技术存在流水线处理器功耗高、全局时钟偏移严重、时钟频率受限制速度慢的问题。

本成果提供了一种基于异步单轨的流水线处理器,各个模块之间通过异步单轨握手完成数据通信,其中异步控制模块包含多个控制单元,所述多个控制单元为多个相位解耦Click单元,所述多个相位解耦Click单元通过握手相互级联,并分别与对应的流水线连接。本成果解决了相关技术中流水线处理器功耗高、全局时钟偏移严重、时钟频率受限制速度慢的问题,实现了流水线在低功耗下无时钟以较高速度运行。

合作需求

技术转让、技术许可

成果二:一种基于深度学习技术的视觉辅助系统

所属领域

人工智能技术

成果简介

视觉障碍人群、视觉受损人群存在出行不便性,近年来,随着这类人群数量的增长,人们对视觉辅助系统的需求更加强烈。基于深度学习技术的目标检测算法在应用于视觉障碍人群、视觉受损人群外出出行场景时,多变的道路场景以及多形态的目标要求系统具有较高环境感知性能,且要求对复杂的外界环境有较强的鲁棒性。复杂的处理过程、较高的计算成本以及较高的系统功耗,使得视觉辅助系统难以实现高性能检测和超长续航。

本成果提供了一种基于深度学习技术的视觉辅助系统,包括数据采集单元、数据预处理单元、环境感知单元和用户接口单元,其中数据采集单元用于感知周围环境的信息,并将感知到的数据传输至数据预处理单元;数据预处理单元对接收到的数据进行预处理,然后将预处理好的数据传输至环境感知单元;环境感知单元接收数据后进行基于深度学习技术的障碍物检测,得到周围环境中障碍物的类别、位置及距离,然后将检测到的周围环境的障碍物信息处理成文本信息,并将文本信息送入用户接口单元;用户接口单元将文本信息转化成语音,供用户获知周围的环境的障碍物情况。该系统很好的满足了视觉辅助系统辅助出行的应用场景。

合作需求

技术转让、技术许可

成果三:一种深度学习芯片的全异步存储系统及其生产方法、设备

所属领域

集成电路技术

成果简介

目前,使用专用集成电路(ASIC)作为载体实现深度学习算法网络的功能时,通常会遇到以下两个问题:第一是每一次的网络推理都有可能执行上亿次操作,计算量十分庞大;第二是需要存储、利用海量的参数,存储访问非常密集。因此,该领域内的芯片要求系统具有快速访问存储以及降低访问功耗的能力。

传统的深度学习芯片采用的是同步电路的设计方法,同步电路具有成熟的EDA工具链支持,其设计相对于异步电路简单得多。但随着制造工艺的发展,特别是特征尺寸到了亚微米时代,同步电路的设计和制造面临着很多棘手的问题:例如高速的同步电路存在时钟偏移、时钟抖动、时序难以收敛、鲁棒性差和设计复杂度提高等问题。此外,同步电路所有的事件触发均由时钟信号来控制,由于每次都要等待时钟沿的到来才触发,这样将浪费大量的时间,访问速度受到限制,很难实现高性能。时钟树的功耗和面积对芯片带来了额外的开销,同样也很难实现低功耗。然而而异步电路设计相对复杂,异步电路EDA的开发需要资金、市场等等因素的驱动,目前仍然缺乏成熟的商用异步电路EDA工具链,导致异步电路的制造非常缓慢,难以推广。现有技术中存在的这些问题亟待解决。

本成果提供了一种深度学习芯片的全异步存储系统及其生产方法、设备。采用异步电路的通信模式来搭建所述存储系统,各个模块之间采用请求-应答信号进行通讯,摒弃了同步电路依赖全局时钟触发事件的形式,使得运行速度不受限于关键路径,处理性能得到了提升本。成果有效规避了复杂的时钟树设计,将可以很大程度降低芯片的面积和功耗,还可以规避时钟偏移、抖动的问题,兼具高性能、低功耗、鲁棒性强、可移植性好、模块化程度高和电磁兼容性强等优点。本成果用于深度学习芯片中可有效达到高性能、低功耗的目标,可广泛应用于集成电路技术领域。

合作需求

技术转让、技术许可

成果四:一种可配置、可重构的逻辑计算系统芯片及控制方法

所属领域

集成电路技术

成果简介

计算机技术、数据处理技术、人工智能技术等作为信息化载体,带来了指数级递增的数据计算量、超高速的计算速度需求和超低功耗的便携式嵌入系统的应用需要。如何发展和实现低功耗、高速度、高稳定性的集成电路系统已经成制约现代社会发展的一大关键问题。

CMOS作为传统的集成电路基础元器件,数十年来一直遵循着 “摩尔定律” 的发展规律。CMOS工艺向着10nm节点之下发展时,其被物理极限和生产技术所限,器件本身受到量子效应和短沟道效应的影响越来越严重,泄漏电流增加、器件稳定性降低,更小尺寸的开发技术成本增高,尺寸缩小带来的性能红利已基本丧失。并且VLSI系统中随着尺寸缩小而增长的寄生电容和电阻更是导致了系统总功耗显著增加、全局互联延迟增加、整体稳定性逐步降低。此外,现在主流的计算架构大多为存储和处理器分离开来的冯诺依曼架构,中央处理器本身不具备数据存储的功能,其输入(输出)来自于(写入)缓存或者内存等存储单元,这就导致了大量的功耗浪费在了频繁的处理器与存储之间的数据交互上。另外由于不同的存储等级之间存在速度差异、数据传输和逻辑运算之间存在速度差,导致计算机逻辑运算的整体速度受限,此为现代计算架构固有的“存储墙”和“功耗墙”问题。

本成果开发了一种可配置、可重构的逻辑计算系统、芯片及控制方法,通过灵活构建逻辑MTJ树和参考MTJ树,可使一种计算架构附加简单的配置信号实现多种逻辑输出,而且利用磁隧道结的存储与计算一体实现了数据的原位计算,避免了数据频繁迁移造成的高功耗、互联延迟等问题的产生,同时采用时间迭代中间逻辑的循环运算方式替代传统CMOS简单逻辑门的级联,实现了更加复杂的运算,极大地节省硬件资源,降低嵌入成本,该成果可广泛的应用于集成电路领域。

合作需求

技术转让、技术许可

合作需求

合作研发、技术转让

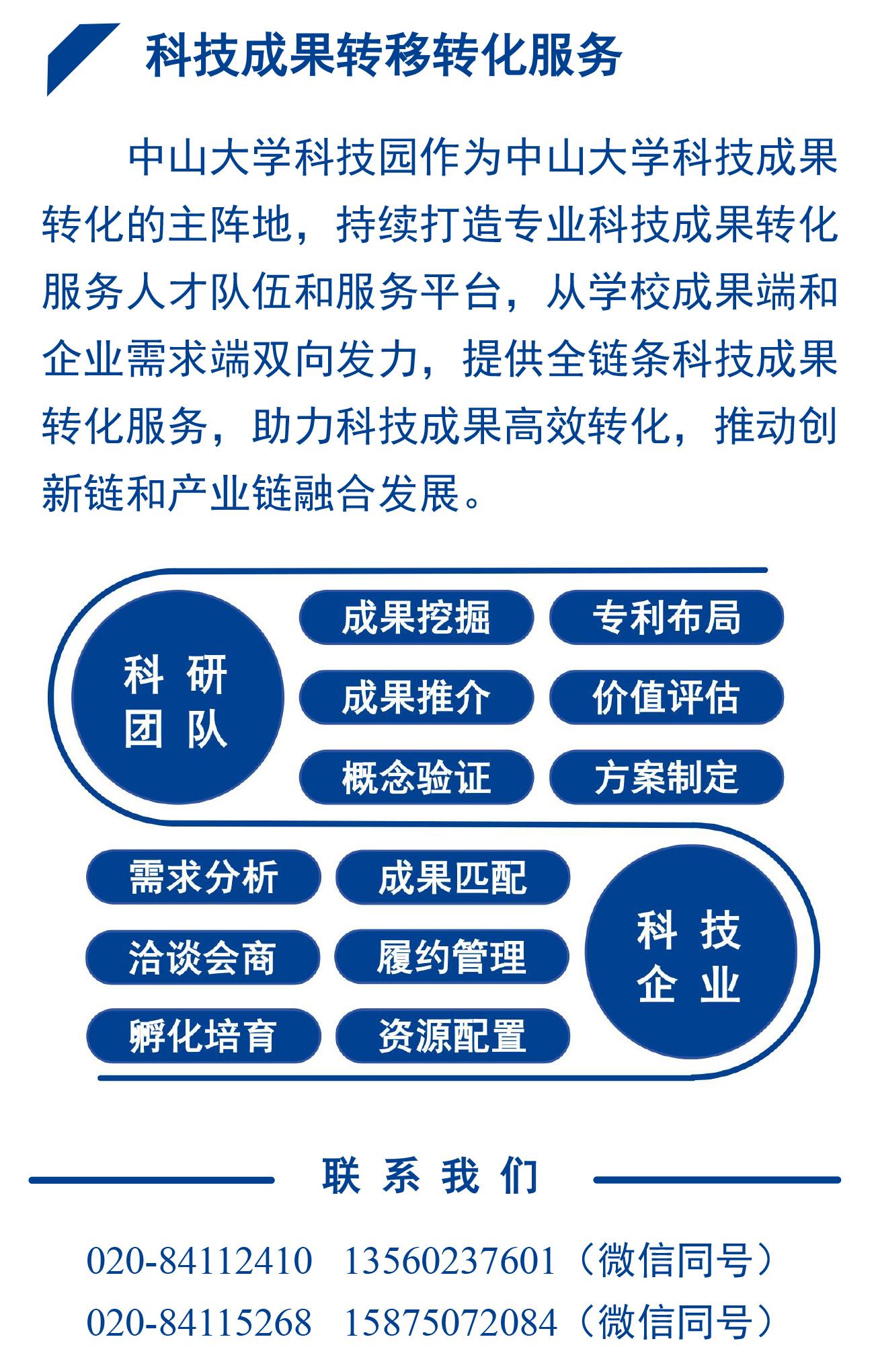

如您有成果发布或成果对接意向,欢迎联系

秦杰

020-84112410,13560237601

陈湘鹏

020-84115268,15875072084